## Latch-Up and Overcurrent **Protection System**

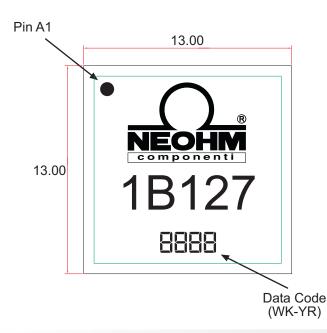

# 1 B 12 7

#### **FEATURES**

- Wide Supply voltage range: 2.7 36V

- Low power consumption

- · Maximum current: 2 A

- Programmable current threshold

- · Only one external resistor required

- · Wider voltage and current range with external transistor

- · Load disable input

- Current monitor output

- · Programmable off time (with external capacitor)

- Filters out inrush current (with external capacitor)

- Controlled slew-rate (with external capacitor)

- Guaranteed radiation tolerance up to 30krad TID

- Wide temperature range: -40°C to +125°C

#### APPLICATIONS

- · Latch-up monitoring and protection systems

- Overcurrent protection

- · Load switch with over-current monitoring

- Load switch with slew-rate limitation

- Protects low-cost devices from latch-ups

#### **IDESCRIPTION**

Latch-up is a catastrophic phenomenon which affects CMOS devices. It is caused by high energy particles or ionizing radiations or other causes which trigger the parasitic transistors, mostly in CMOS devices that are not radiation-hardened.

The 1B127 is a latch-up and overcurrent protection system suited for high radiation level environments, such as Low Earth Orbit satellites.

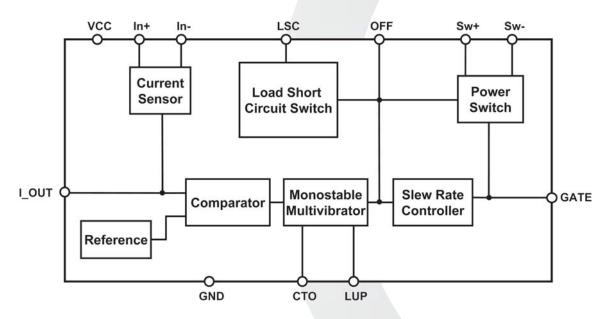

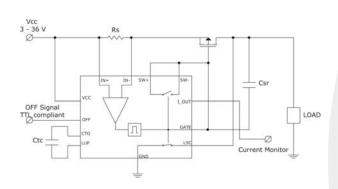

Figure 1. Block diagram.

UNI EN ISO 9001: 2000

It allows using low-cost devices (COTS) in radiation environments like space applications, high-energy physics experiments and biomedical equipment, by protecting them against the effects of latch-up. The system monitors the current flowing through an external sense resistor (Rs) and whenever a threshold value is reached the internal pass transistor switches off the load. After a user-defined recovery time, the pass transistor automatically turns on again restoring power supply to the load, once the latch-up has faded away.

The device can also be used as a current-limited load switch by sending a TTL signal to the OFF pin. For higher voltages or currents, an external PMOS pass transistor can be used.

Inrush current effects or short current spikes can be filtered away. Allowed inrush charge and recovery time can be set using external capacitors.

In addition, the slew-rate while turning on load supply voltage can be limited using an external capacitor to program the inrush current.

The device is available in a small 13x13 mm plastic 100BGA package and it is available for the extended temperature range (-40 °C to +125 °C). It has a low quiescent current, which makes it suitable for low power systems.

#### **ABSOLUTE MAXIMUM RATINGS**

-0.3V ÷ 36V Supply voltage (VAL) Analog Input Vin+, Vin-Vcc-0.3V÷Vcc+0.3V -40V ÷ 2V Differential voltage -0.3V ÷ 36V **OFF** input Internal Load Switch Max V 18V Load Curr. with Internal Switch 2A 300mA Max current sink -40°C ÷ +125°C -50°C ÷ +150°C **Operating Temperature** Storage Temperature Junction Temperature +150°C

#### **OPERATION**

The 1B127 device (see block diagram in fig. 1) monitors the current on the high side by measuring the differential voltage across a shunt resistor (pins IN+ and IN-). The floating differential voltage is transformed into a ground-referenced voltage on the I\_OUT pin. An external capacitor connected to the I\_OUT pin allows filtering short current spikes, while an external resistor connected to the same pin allows changing the gain of the current monitor.

A comparator detects when the current overpasses a threshold value, triggering a monostable for a fixed time period. An external capacitor across pins CTO and LUP allows to increase that time period.

The output of the monostable (which is available as a logic signal on the LUP pin) turns off the internal power switch (across SW+ and SW- pins), disconnecting the load from the power supply. An additional output LSC optionally sinks current from the load, when load supply is removed, to discharge capacitors which might be present on the load or to sink leakage currents which might come from other input/output connections of the load.

After the monostable resets to its normal condition, the power switch is turned on again to supply power to the load. The slew-rate controller optionally limits The OFF pin may optionally turn load power off under user control.

The control of the power switch is also available via the GATE pin to drive an external power transistor, augmenting load voltage or load current capabilities.

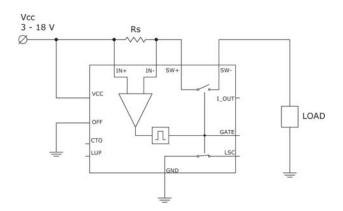

Figure 2 shows the basic configuration of the circuit,

$$R_{S} = \frac{V_{th}}{I}$$

Where I is the current through the sense resistor (that is, load current), and Vth is the device threshold voltage. The power rating of this resistor shall be at least:

$$P_{R_S} = \frac{V_{th}^2}{R_S}$$

The I OUT voltage can be calculated as:

$$V_{I OUT} = I \cdot R_{S} \cdot Gain$$

where nominal Gain without ext components is 30.

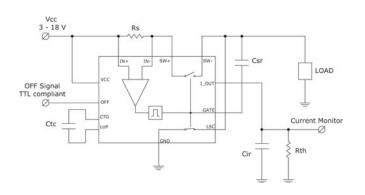

The Gain can be modified (together with threshold voltage) as shown in fig. 3, by adding an external resistor Rth:

$$R_{G} = rac{R_{th}R_{OUT}}{R_{th} + R_{OUT}}$$

$$Gain = rac{R_{G}}{5k\Omega}$$

$$V_{th} = rac{600mV}{Gain}$$

where ROUT is the output impedance of the I\_OUT output (nominal value 150k).

By adding the CIR capacitor, as shown in Figure 3, the I\_OUT is filtered by a low-pass filter with cut-off frequency of:

$$f_T = \frac{1}{2\pi (C_{IR} + 100pF) \cdot R_G}$$

allowing an inrush charge without triggering of:

$$Q = \frac{(C_{IR} + 100pF) \cdot 3kV\Omega}{R_S}$$

Adding the CTC capacitor, as shown in Figure 3, the recovery time can be increased according to the following equation:

$$C_{TC} = \frac{T_{OFF}}{100k\Omega} - 100nF$$

To control the slew-rate of load voltage to prevent high inrush currents into the load, an external capacitor (Csr in Figure 3) can be used and its value is given by:

$$C_{SR} = \frac{T_{rise} - 165us}{33k\Omega}$$

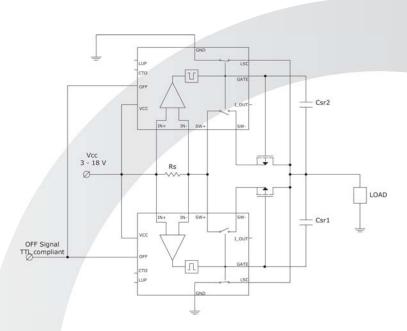

In more than 2A or more than 18V supply voltage are needed, an external PMOS pass transistors can be used (as shown in Figure 4). The external pass transistor is driven by the SW+, SW- and GATE pins shorted together.

In this case the CSR capacitor should be calculated according to the following equation (CG is the external PMOS gate capacitance):

$$C_{SR} = \frac{T_{rise}}{3.3 \cdot 10^4 \Omega} - C_G$$

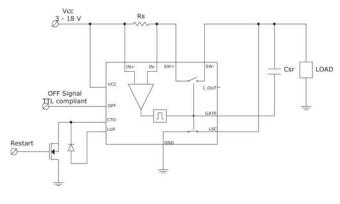

Adding an external diode and transistor as shown in fig. 5, locks the the monostable in this way, once the device has been triggered by an overcurrent, only turning the external MOS on resets the 1B127 device to its normal operation.

Figure 6 shows a fault-tolerant configuration where a pair of 1B127 devices are paralleled to increase fault tolerance. A short circuit on one of the pass transistors (internal or external) and a stuck-open fault on the 1B127 mos driver can be tolerated. In case of stuck-closed on the 1B127 driver the latch-up protection is no more effective but the load can still be turned on.

UNI EN ISO 9001:

#### **ELECTRICAL CHARATERISTICS**

All characteristics at  $T_A$ = 25 °C,  $V_{CC}$  = 5 V, unless otherwise noted.  $V_{sense}$   $V_{in+}$  -  $V_{in-}$

| Parameter                                 | Condition                                             | 1B127      |      |            | Unit           |

|-------------------------------------------|-------------------------------------------------------|------------|------|------------|----------------|

|                                           |                                                       | Min        | Тур  | Max        | Offic          |

| INPUT                                     |                                                       |            |      |            |                |

| Differential Input Voltage                |                                                       |            | 20   | 500        | mV             |

| Common-Mode Input Range                   |                                                       | Vcc -100mV | Vcc  | Vcc +100mV | V              |

| Common-Mode Rejection                     | $V_{in+}$ = 2.7 V to 30 V,<br>$V_{sense}$ = 20 mV (*) | 100        | 120  |            | dB             |

| Threshold voltage V <sub>th</sub>         | without external components                           | 29         | 30   | 31         | mV             |

| over temperature range                    | Without external components                           | 28         |      | 32         | mV             |

| temperature drift                         |                                                       | 20         | 1    | 02         | μV / °C        |

| drift vs. common mode (V <sub>in+</sub> ) | $V_{in+} = 2.7 \text{ V to } 36 \text{ V}$            |            | 0.04 | 4          | μ <b>V</b> / V |

| unit vs. common mode (v <sub>m+</sub> )   | Vin+ - 2.7 V to 30 V                                  |            | 0.04 | 4          | μ <b>ν / ν</b> |

| Input Bias Current                        |                                                       |            | 2    |            | μА             |

| over temperature range                    |                                                       |            |      | 10         | μΑ             |

| POWER SUPPLY                              |                                                       |            |      |            |                |

| Supply Voltage                            | Vcc                                                   | 2.7        |      | 36         | V              |

|                                           |                                                       |            |      |            |                |

| Supply Current                            | Vcc = 3 V                                             |            |      | 200        | μΑ             |

|                                           | Vcc = 5 V                                             |            |      | 360        | μΑ             |

|                                           | Vcc = 15 V                                            |            |      | 700        | μΑ             |

|                                           | Vcc = 36 V                                            |            |      | 2          | mA             |

| POWER SUPPLY                              |                                                       |            |      |            |                |

| Continuous Load Current                   |                                                       |            |      | 2          | Α              |

| Peak Load Current                         | 1 ms pulses, DC < 1%                                  |            |      | 3          | Α              |

| Supply Voltage                            | , ,                                                   | 2.7        |      | 20         | V              |

| Leakage Current                           | -40 °C < T <sub>A</sub> < 125 °C                      |            |      | 100        | μА             |

| TIMING                                    |                                                       |            |      |            |                |

| Turn-off time:                            | Inrush current = 2 Ith                                |            |      | 100        | μS             |

|                                           | $C_{IR} = 0$                                          |            |      |            |                |

|                                           | C <sub>IR</sub> = 2.7 nF                              |            |      | 1          | ms             |

|                                           |                                                       |            |      |            |                |

| Recovery Time                             | without external components                           |            | 10   |            | ms             |

| OUNIX OUR DESIGN                          | C <sub>TC</sub> = 1 nF                                |            | 110  |            | ms             |

| SINK CURRENT                              | V 0=V                                                 | _          |      |            |                |

| Sink Current                              | Vcc = 2.7 V                                           | 5          |      | 00         | mA             |

|                                           | Vcc = 15 V                                            |            |      | 36         | mA             |

| Peak Current                              | 1 ms pulses, DC < 1%                                  |            |      | 500        | mA             |

| I_OUT                                     |                                                       |            |      |            |                |

| Gain, without external components         |                                                       | 29         | 30   | 31         |                |

|                                           | over Temperature                                      | 28         | 30   | 32         |                |

| Output Impedance Rout                     |                                                       |            | 150  |            | KW             |

| Output Swing                              |                                                       |            | 0.6  |            | V              |

| THERMAL                                   |                                                       |            | 0.0  |            | •              |

| Thermal Resistance between power          |                                                       |            |      |            |                |

| switch junction to balls                  | Thermal Resistance <b>q</b> <sub>JC</sub>             |            | 12   |            | °C / W         |

| Thermal Resistance between power          | Thermal Resistance q <sub>JA</sub>                    | 1          |      |            |                |

| switch junction to ambient                | Mounted on std 1.6mm PCB                              |            | 34   |            | °C / W         |

| ESD                                       |                                                       |            |      |            |                |

|                                           |                                                       |            |      |            |                |

| All Pins                                  | HBM 1.5K <b>W</b> , 100pF                             | 2          |      |            | ΚV             |

|                                           | ,                                                     |            |      |            |                |

Tel: +39 011 9974022 Fax: +39 011 9974982

#### **APPLICATION DIAGRAMS**

Figure 2. Basic device configuration.

Figure 5. Current protection with restart signal.

Figure 3. Circuit with Toff and Slew-Rate control.

Figure 4. Circuit with an external Pass Transistor to increase load current.

Figure 6. Fault-tolerant configuration with two parallel branches and two series transistors.

#### TYPICAL CHARACTERISTICS

All characteristics at  $T_A$  = 25 °C,  $V_{CC}$  = 5 V, unless otherwise noted.

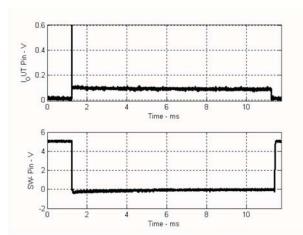

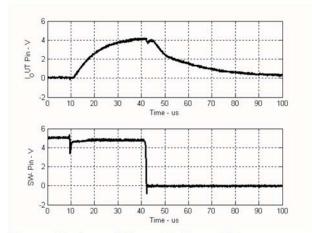

Figure 7. Latch-up event with  $V_{CC} = 5 \text{ V}$ .

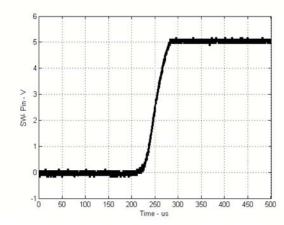

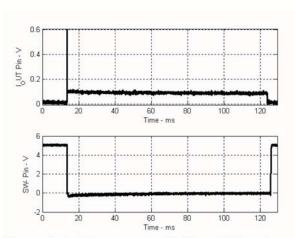

**Figure 9.** Turn-on time with  $V_{CC}$  = 5 V and no external component.

Figure 11. Turn off time with  $V_{CC} = 5 \text{ V}$ .

**Figure 8.** Latch-up event with  $V_{CC} = 5 \text{ V}$  and  $C_{TC} = 1 \text{ uF}$ .

**Figure 10.** Limited slew-rate with  $V_{CC}$  = 5 V and  $C_{SR}$  = 2.7 nF.

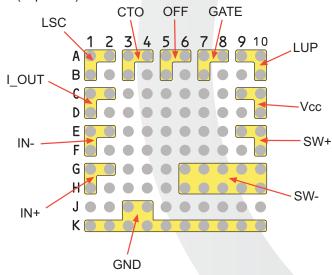

#### IPINS DESCRIPTION

| PIN Name | Documentation                                                                                                                                                                                                                                                               |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND      | GROUND pin for the device                                                                                                                                                                                                                                                   |

| GATE     | OUTPUT: to be connected to the gate of the external PMOS transistor, when used. It is also used to connect an optional external capacitor to limit slew-rate of the <b>SW-</b> pin. It can also be used to connect an optional external resistor to reduce slew-rate.       |

| LSC      | POWER: load sink. Sinks a current from load during a latchup condition.                                                                                                                                                                                                     |

| VAL      | SUPPLY pin for the device                                                                                                                                                                                                                                                   |

| сто      | INPUT: positive terminal of capacitor to set the turn-on time. The other terminal should be connected to <b>LUP</b> pin.                                                                                                                                                    |

| SW-      | POWER: negative side of load power switch. It should be connected to the load, except when an external PMOS transistor is used. It can also be used to connect an optional external capacitor to limit the slew-rate of the <b>SW-</b> pin.                                 |

| SW+      | POWER: positive side of load power switch. It should be connected at the negative side of external shunt resistor, except when an external PMOS transistor is used                                                                                                          |

| LUP      | OUTPUT: set at logic-1 when a latchup or overload condition has been detected. Remains high for the whole turn-on time. Logic-1 level is coincident with supply voltage. It can also be used to connect an optional external capacitor to set the turn-on time.             |

| I_OUT    | OUTPUT: Ground-referenced voltage proportional to the load current. When load power is turned off due to a latchup or overload condition, output voltage is unpredictable. It can also be used to connect an optional external capacitor to set the allowed inrush current. |

| OFF      | INPUT: load enable. When at logic-1 enables load power supply. When al logic-0 turns load power off                                                                                                                                                                         |

| IN-      | INPUT: negative side of external shunt resistor. It should be connected to the Load via the Power Load Switch.                                                                                                                                                              |

| IN+      | INPUT: positive side of external shunt resistor. It should be connected to power supply generator.                                                                                                                                                                          |

### PINS LAYOUT (Top View)

#### **NEOHM COMPONENTI S.r.I.**

Tel: +39 011 9974022 Fax: +39 011 9974982

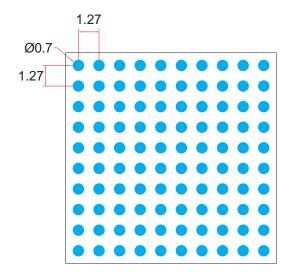

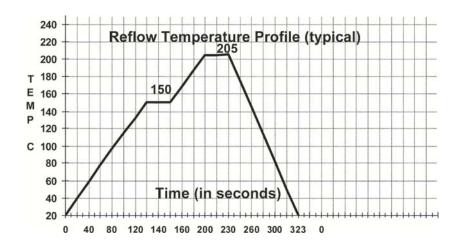

#### SOLDERING PATTERN

#### SOLDERING PRECAUTIONS

Before soldering put the 1B127 in oven @ 50° for 30 minutes

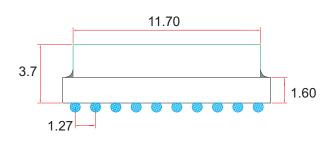

#### **PACKAGE OUTLINE**

(All dimensions are in mm)

#### I ESD SENSITIVITY

The device can be damaged by ESD: we suggest to handle all integrated circuits with appropriate precautions.

Total or partial failure of the system can be originated by wrong installation and handling procedures.

#### **ACKNOWLEDGEMENTS**

This device has been designed in cooperation with the Space Avionics Technology Center of Dept. of Electronics of Politecnico di Torino, and is supported by project MAESS funded by Regione Piemonte (I).

Tel: +39 011 9974022 Fax: +39 011 9974982

#### **DISCLAIMER**

Neohm products are not authorized for use in safety-critical applications (such as life support) where a failure of the Neohm product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Neohm products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by Neohm. Further, Buyers must fully indemnify Neohm and its representatives against any damages arising out of the use of Neohm products in such safety-critical applications.